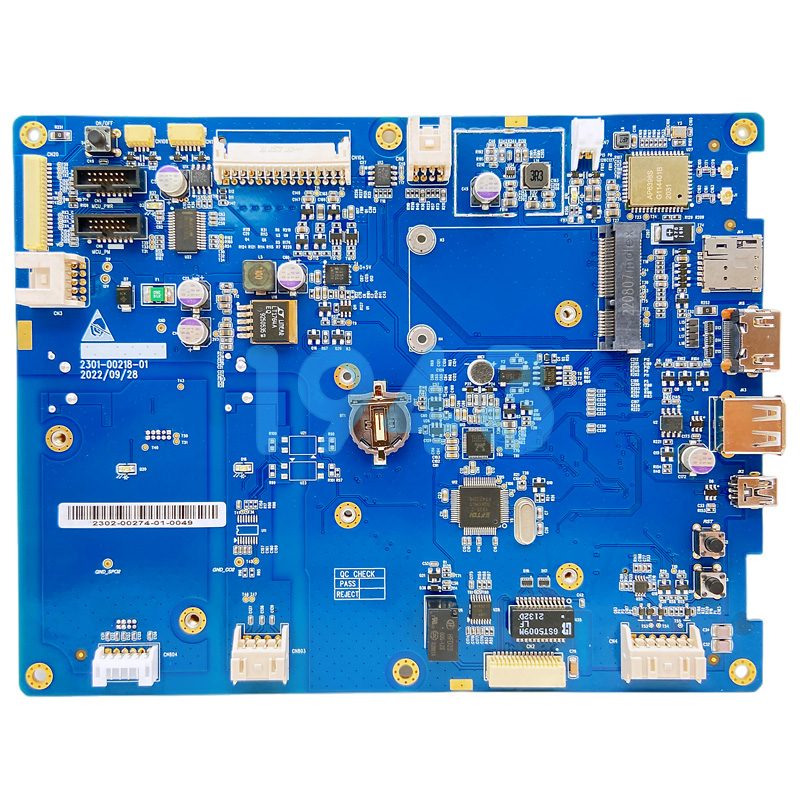

封装不是“外壳”,而是芯片与 PCB 的“婚姻介绍所”。选错封装,要么信号跑不动,要么散热扛不住,要么工厂做不出来。深圳SMT贴片加工厂-1943科技把时间轴拉到 1970-2025,用工程师的视角,把 DIP、SOP、QFP、BGA 串成一条线,告诉你它们为什么诞生、怎么落地、现在还能不能买。

1. 1970s:DIP —— 手工焊接的“最后乐园”

- 结构:两排直插引脚,0.1 inch(2.54 mm)标准间距。

- 优点:

- 面包板可插,实验室最爱;

- 电烙铁 320 ℃ 就能焊,返修零成本。

- 硬伤:

- 引脚>40 时,PCB 面积爆炸;

- 引脚电感≈7-10 nH,跑 50 MHz 以上信号直接翻车。

- 现状:

- 2025 年仍能在工控板、教学板上看到,但主流代工厂已把 DIP 列为“特殊工艺”,价格反而比贴片贵 15-20%。

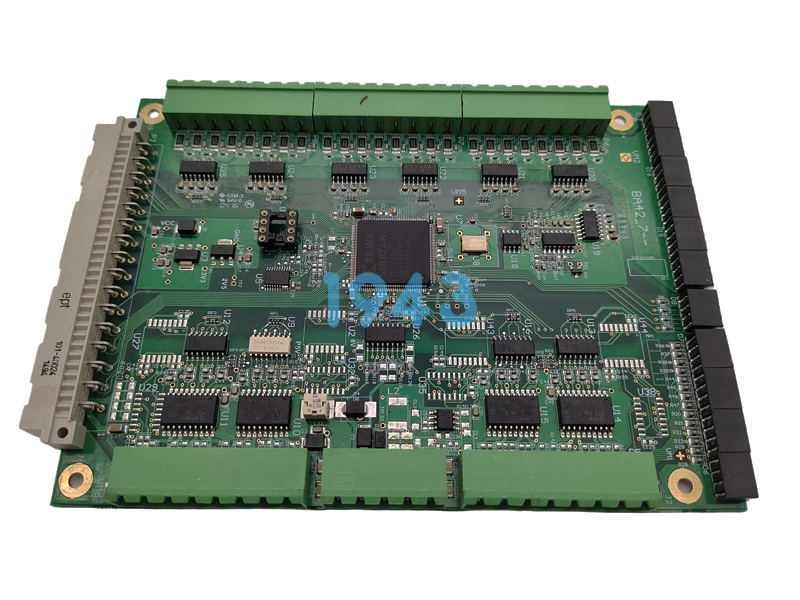

2. 1980s:SOP/TSOP —— 把“翅膀”贴在板子上

- 进化点:引脚改成 L 型贴装,间距缩到 1.27 mm → 0.65 mm。

- 红利:

- 面积缩小 50%;

- 寄生电感降到 3-5 nH,能跑 100 MHz。

- 痛点:

- 四周引脚数极限≈128;

- 散热靠引脚,功耗>1 W 芯片直接烫手。

- 今天还能怎么用:

- 存储器(NOR Flash)、低速 MCU,打样阶段用 TSOP48/56 仍是“交期最短”的方案。

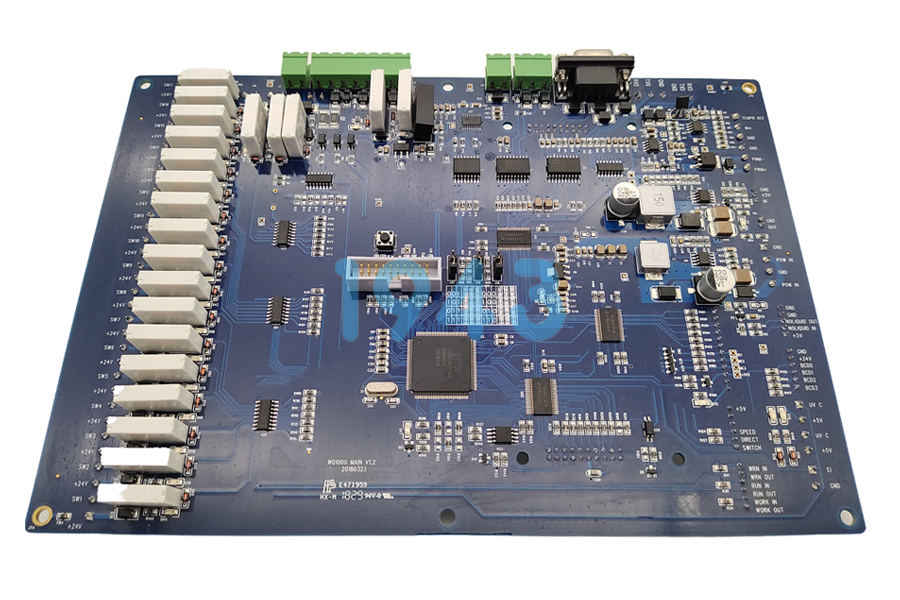

3. 1990s:QFP —— 把“四边”都插上引脚

- 结构:四侧鸥翼引脚,间距 0.5 mm 主流,极限 0.3 mm。

- 高光时刻:

- STM32F103、早期 ARM7 全系 QFP;

- 引脚数突破 256,跑 200 MHz 以内没问题。

- 暗礁:

- 0.3 mm pitch 的板厂成本飙升;

- 引脚易变形,SMT 线必须配 AOI。

- 2025 年现状:

- 中低端 MCU、驱动 IC 仍在用;

- 但凡是 >256pin 的新品,全部转向 BGA/LGA。

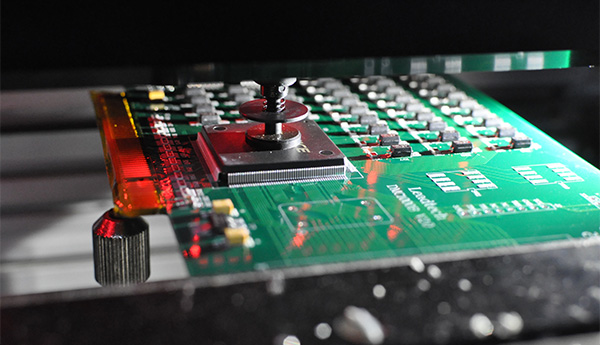

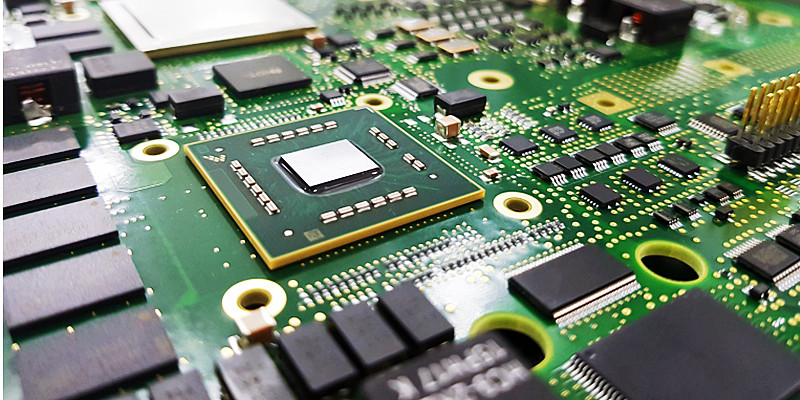

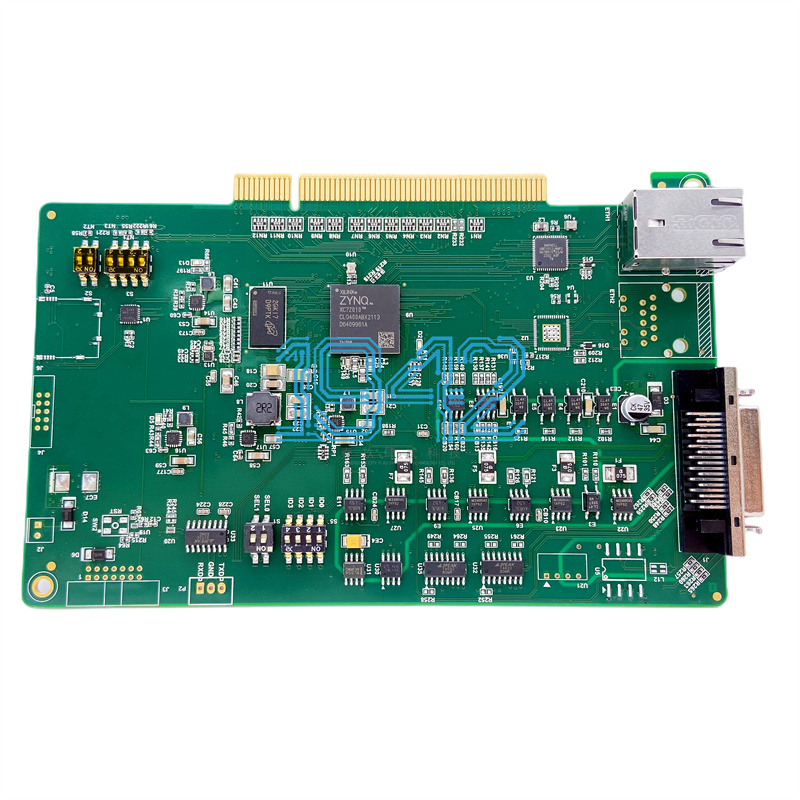

4. 2000s-2025:BGA —— 把引脚“藏”到肚子下面

- 结构:底部阵列锡球,pitch 0.8 mm → 0.5 mm → 0.4 mm;

- 为什么非用不可:

指标 QFP256 BGA256 备注 封装面积 28×28 mm 17×17 mm 节省 60% 面积 寄生电感 5-7 nH/引脚 <1 nH/球 信号>1 GHz 必须 BGA 散热路径 只靠引脚 中心可加散热焊盘 5 W 以上芯片稳了 - 制造门槛:

- PCB 至少 6 层,激光盲孔是标配;

- 回流焊曲线窗口窄,X-Ray 检测不可省。

- 返修现实:

- 需要 BGA 返修台 + 红外预热 + 氮气;

- 一次返修 15 分钟,成本≈¥30-50/颗。

5. 选型口诀

- ≤32pin、低频、手焊:直接 DIP 或 SOP,别折腾。

- 32-128pin、<200 MHz:QFP 仍是“交期最短、设备最通用”的平衡点。

- ≥144pin、高速或高功耗:毫不犹豫 BGA,PCB 预算提前翻倍。

- 量产>5万:优先考虑 QFN/DFN,比 QFP 省面积,比 BGA 省成本。

6. 写在最后

封装演进没有“谁淘汰谁”,只有“谁更适合当下需求”。

2025 年的今天,DIP 还在教学板发光发热,BGA 已在 5G 基站里跑 112 Gbps PAM4。

下次选型前,先问自己三个问题:

- 信号跑多快?

- 芯片热多大?

- 工厂产线能不能做?

把这三个答案对上号,封装就选对了一大半。

2024-04-26

2024-04-26