以下是针对工业 PLC 模块 PCBA 实现微秒级实时信号传输延迟优化的技术方向梳理,结合硬件设计、协议优化、软件架构及系统协同等维度:

一、硬件设计与信号完整性优化

-

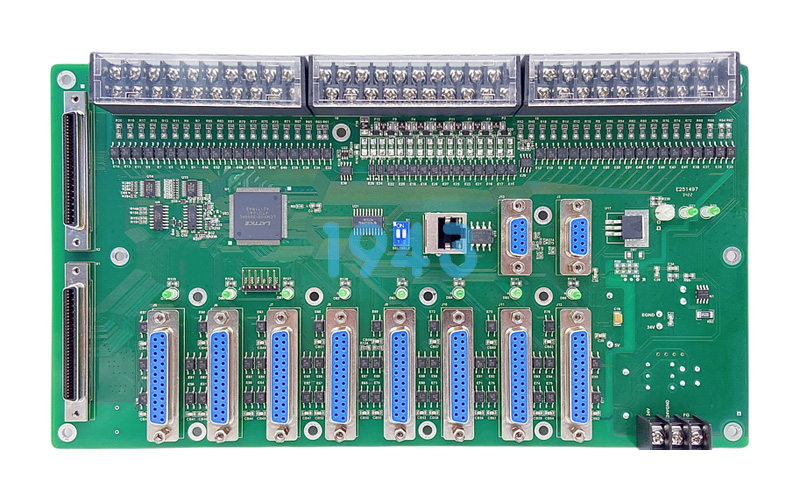

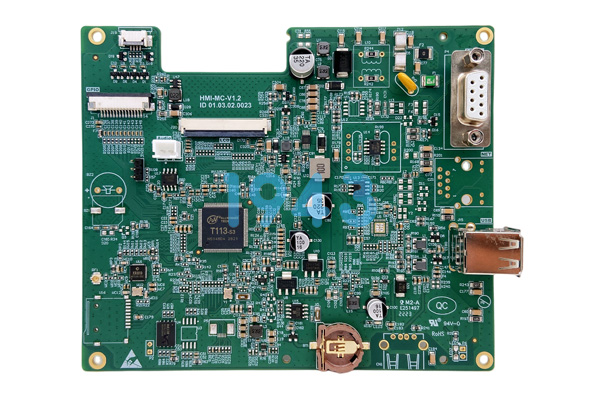

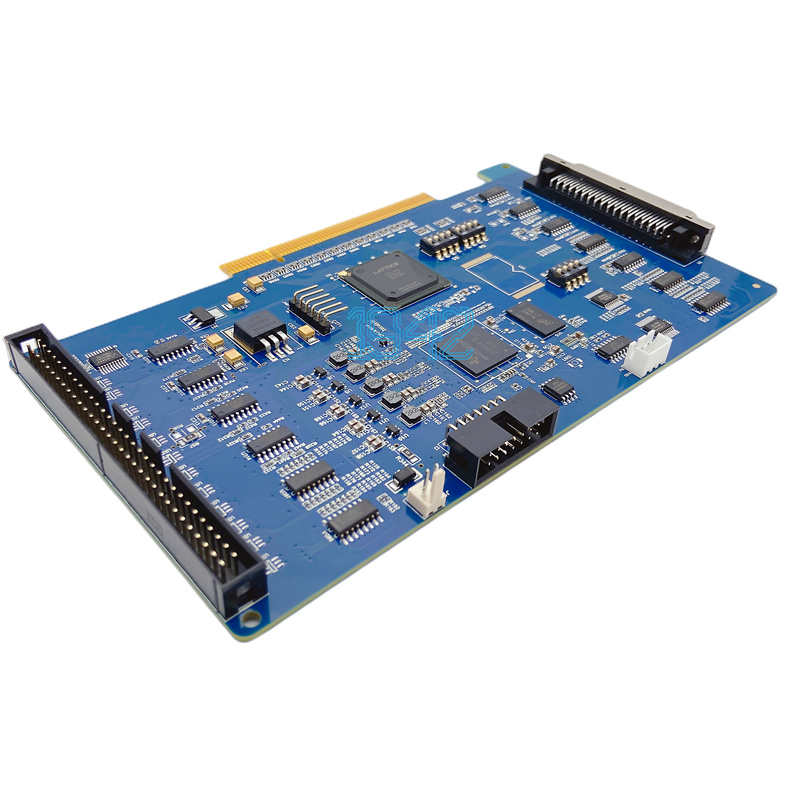

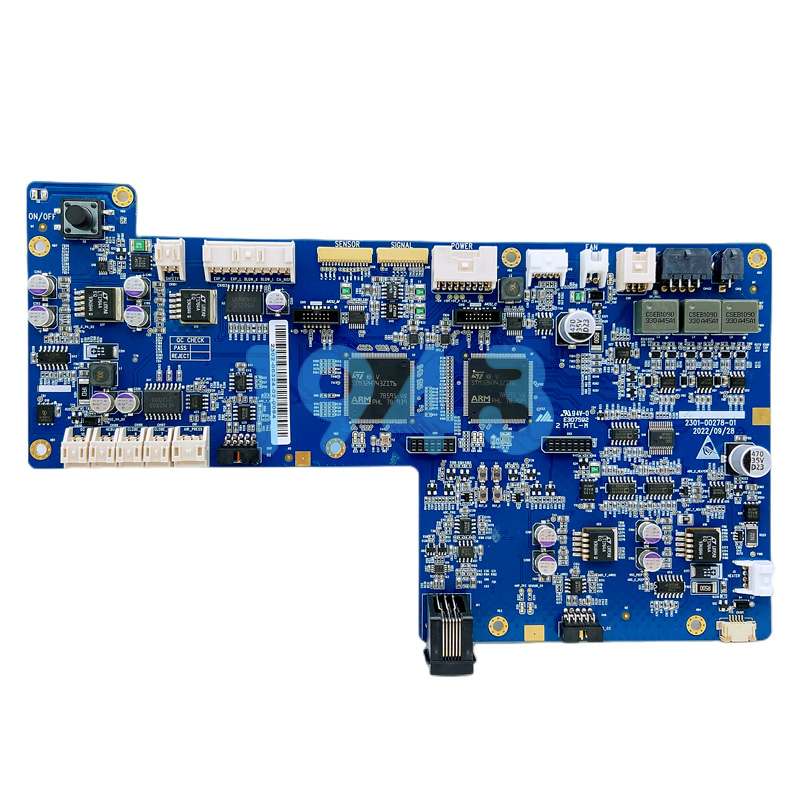

高速器件选型与接口匹配

- 采用低延迟微控制器(如 ARM Cortex-R 系列、专用实时控制芯片)与高速接口芯片(如支持 SERDES 的 FPGA/ASIC、EtherCAT 从站控制器 ESC)。

- 关键信号链路(如时钟、同步信号、高速数据总线)匹配传输线阻抗(如 50Ω/90Ω 差分阻抗),减少信号反射与畸变。

-

PCB 布局与布线策略

- 高速信号(如 LVDS、HDMI、工业以太网差分对)采用短路径、少过孔设计,避免跨层交叉,优先使用内层带状线降低 EMI。

- 时钟信号独立隔离,差分对严格等长(误差<5mil),电源层与地层紧密耦合,减少电源噪声对信号的干扰。

-

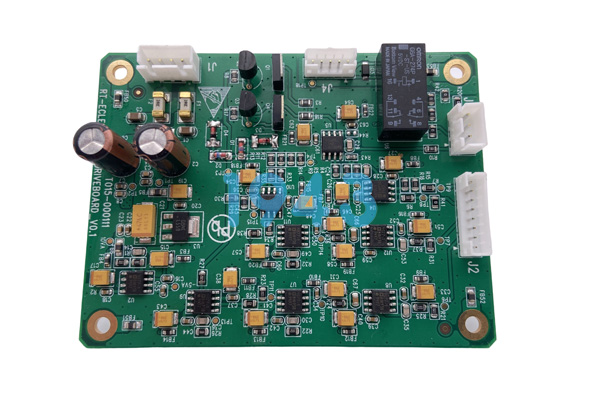

硬件加速与缓存机制

- 集成硬件加速器(如专用通信协处理器、DMA 控制器)分担 CPU 负载,实现数据零拷贝传输。

- 配置片上高速缓存(Cache)或片外 SRAM,减少主存访问延迟,提升数据处理效率。

二、实时通信协议与链路优化

-

低延迟协议选择与定制

- 采用实时以太网协议(EtherCAT、Profinet RT/IRT、Ethernet/IP CIP Sync)或专用总线(CAN FD、SERCOS III),支持微秒级循环周期。

- 定制轻量化应用层协议,精简数据帧头(如省略冗余校验字段),减少协议解析开销。

-

网络架构与同步机制

- 星型 / 环型拓扑降低网络跳数,配合交换机端口硬件时间戳(如 IEEE 1588 PTP 精确时钟同步),实现亚微秒级时钟同步精度。

- 硬件时间戳标记信号收发时刻,避免软件中断处理引入的延迟抖动。

三、软件架构与实时性优化

-

实时操作系统(RTOS)与任务调度

- 选用确定性调度 RTOS(如 QNX、RTX、VxWorks),配置抢占式优先级调度,关键任务(如通信中断处理)设为最高优先级,禁止不必要的任务切换。

- 最小化中断服务程序(ISR)执行时间,将数据处理移至后台任务(Task),减少中断嵌套深度。

-

驱动与协议栈优化

- 硬件驱动采用轮询(Polling)与中断结合模式,对高速数据链路(如以太网)使用零拷贝技术(Zero-Copy)避免数据复制延迟。

- 协议栈内核态实现,减少用户态 - 内核态上下文切换,或通过 FPGA 硬逻辑实现部分协议处理(如 CRC 校验、数据成帧)。

-

算法与数据处理轻量化

- 避免动态内存分配(如使用静态内存池),数据预处理在硬件层面完成(如 ADC 采样直接存入 DMA 缓冲区)。

- 采用高效数据结构(如环形缓冲区)减少数据拷贝,对实时信号禁用浮点运算,转为定点数处理降低计算延迟。

四、系统级协同与验证

-

端到端延迟建模与仿真

- 使用信号完整性仿真工具(如 HyperLynx、Cadence Sigrity)预测 PCB 布线延迟,结合时序分析工具(如 Synopsys PrimeTime)评估芯片内部流水线延迟。

- 构建硬件在环(HiL)测试平台,模拟工业现场环境(如高温、振动)下的延迟稳定性。

-

同步与抖动抑制

- 外部输入同步信号(如 10MHz 参考时钟)经锁相环(PLL)倍频生成系统时钟,减少时钟抖动对信号采样的影响。

- 对异步通信接口(如 UART)增加 FIFO 缓冲,平滑数据输入输出速率差异。

-

量产一致性控制

- 关键器件(如晶振、PHY 芯片)筛选频率偏差<50ppm,回流焊后校准时钟偏移,确保模块间延迟一致性。

- 自动化测试设备(ATE)批量测量信号环路延迟(如发送 - 接收时间差),剔除超标的 PCBA。

五、环境适应性与可靠性

- 温度补偿:针对工业宽温(-40℃~+85℃)场景,通过温度传感器实时调整时钟频率补偿器件延迟漂移。

- EMC 强化:接口端增加 ESD 保护器件(如 TVS 二极管)、共模电感滤除高频噪声,避免干扰导致的重传与延迟波动。

通过上述多维度技术协同,可将工业 PLC 模块 PCBA 的端到端信号传输延迟控制在微秒级,满足高精度实时控制(如运动伺服、过程同步)的严苛需求。

因设备、物料、生产工艺等不同因素,内容仅供参考。了解更多smt贴片加工知识,欢迎访问深圳smt贴片加工厂-1943科技。

2024-04-26

2024-04-26